# 半导体集成电路 TT335型数字信号处理器

## 数据手册

(202308版)

## 1 产品简介

TT335 是自主研制的高可靠 32 位浮点控制型数字信号处理器, 采用哈佛总线结构, 主时钟工作频率 150MHz, 支持 16\*16 位和 32\*32 位乘加运算, 集成了大容量的片上 Flash 和 SRAM 存储器,以及多种增强的控制外设和支持单精度 IEEE-754 标准的浮点运算单元,为高精度数据分析处理、电机运动控制等应用提供了良好的平台。

相比同档次进口型号产品, TT335 具有以下优势:

- (1) 功耗更低。在内核 1.8V 即可达到 150MHz(全温区), 典型功耗降低 25%以上;

- (2) 性能更强。同频率下定点和浮点程序执行速度提高 5%~30%;

- (3) 安全可靠性更高。消除了原来存在的硬件断点/单步、 RPTB、 Limp 模式等隐藏错误,修补了进口芯片的数据安全漏洞。

## 2 适用范围

除特别声明外,本文档内容适用于TT335所有具体型号产品(不同封装类型)。

## 3 产品特点

#### 3.1 产品功能

TT335 主时钟工作频率 150MHz, 片内集成了多种增强的控制外设和支持单精度 IEEE-754 标准的浮点运算单元, 为高精度复杂数据的分析处理、电机其他运动控制领域应用的实现提供了良好的平台。 其代码和指令与 F28x 系列数字信号控制器完全兼容, 从而保证了项目或产品设计的可延续性。

TT335数字信号控制器集成了 256K\*16 的 Flash 存储器,8K\*16 的引导 ROM,数字运算表以及 1K\*16 的 OTP ROM,数据及程序存储量大,有效地改善了应用的灵活性。128 位的密码保护机制有效地保护了产品的知识产权。16 通道高性能 12 位 ADC 模数转换单元提供了两个采样保持电路,可以实现双通道信号同步采样。具体指标如下:

- 1) 高性能静态 CMOS 技术

- 标准主频 150MHz(6.67ns 周期时间)

- 内核电压 1.8V, I/O 引脚电压 3.3V

- 2) 高性能 32 位 CPU

- IEEE-754 单精度浮点运算单元(FPU)

- 16\*16 位和 32\*32 位乘加(MAC)

- 16\*16 双 MAC

- 哈佛(Harvard)总线结构

- 快速中断响应和处理

- 统一存储器编程模式

- 可用 C++和汇编语言进行高效编程

- 3) 6 通道 DMA 处理器(用于 ADC、McBSP、ePWM、XINTF 和 SARAM)

- 4) 16 位或 32 位的外部接口(XINTF)

- 超过 2M\*16 的地址范围

- 5) 片内存储器

1

- 256K\*16 的 Flash 存储器

- 34k\*16 的 SARAM

- 1K\*16的OTP(一次性编程)

- 6) 启动 ROM (8K\*16)

- 软件引导模式程序

- 标准的数学表

- 7) 时钟和系统控制

- 片上振荡器

- 看门狗定时器模块

- 8) GPIO0~GPIO63 可以与8个外部内核中 断的任一相连

- 9) 支持全部 58 个外设中断的外设中断扩 展模块(PIE)

- 10) 128 位安全密码

- 保护 Flash/OTP/RAM 存储器

- 防止固件逆向工程

- 11) 增强的控制外设

- 18 个脉宽调制 PWM 输出

- 6 个支持 150ps 微边界定位(MEP) 分辨率的高分辨率脉宽调制器

- (HRPWM) 输出

- 6个事件捕捉输入(CAP)

- 2个正交编码器通道(OEP)

- 8个32位定时器(6个eCAP以及2 个 eQEP)

- 9 个 32 位定时器 (6 个 ePWM 以及 3 个 XINCTR)

- 12) 3个32位CPU定时器

- 13) 串行外设接口

- 2 个控制器局域网(CAN)接口

- 3个SCI(UART)接口

- 2个多通道缓冲串行 McBSP 接口(可 配置为 SPI)

#### 3.2 主要应用领域

- 变频驱动

- 伺服控制

- 数控机床

- 1个SPI接口

- 1 个 I2C 总线接口

- 14) 12 位 A/D 转换器具有 16 个转换通道

- 80ns 的快速转换时间

- 2\*8 通道的多路输入选择器

- 2个采样保持器

- 单次/连续转换

- 内部或外部参考电压

- 15) 可达 88 个独立可复用通用输入/输出 (GPIO) 引脚

- 16) 支持 IEEE 1149.1-1990 标准的 JTAG 边 界扫描

- 17) 先进的仿真功能

- 分析和断点功能

- 硬件实时调试

- 18) 开发支持包括

- ANSI C/C++ 编译/汇编/链接器

- CCS 集成开发环境

- DSP/BIOS

- 数字电机控制和数字电源软件库

- 19) 低功耗模式和节电模式

- 支持 IDLE (空闲)、STANDBY (待 机)及 HALT (停止)模式

- 可独立禁止外设时钟

- 20) 小头 (Little Endianness) 模式

- 21) 封装形式和质量等级

- TT335PQDS: 塑封 LQFP176, 工业 增强级产品

- TT335PBDS: 塑封 PBGA176, 工业 增强级产品

- 22) 温度范围

- -40°C至 125°C

- UPS 电源

- 通信设备电源

- 光伏逆变器

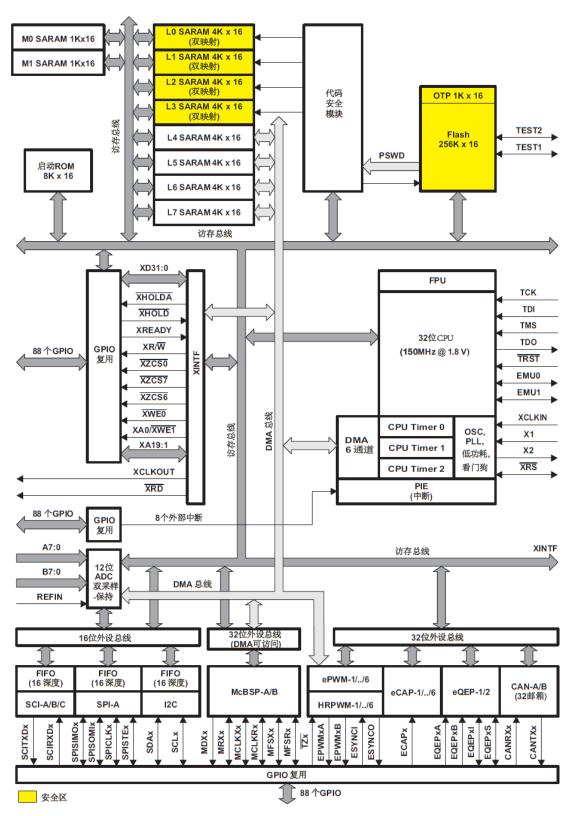

#### 3.3 芯片总体结构

图3-1 TT335组成结构框图

服务电话:008618924645428 008617302669239

# 目 录

| 1 | 产品简介                          | 1  |

|---|-------------------------------|----|

| 2 | 适用范围                          | 1  |

| 3 | 产品特点                          | 1  |

|   | 3.1 产品功能                      | 1  |

|   | 3.2 主要应用领域                    | 2  |

|   | 3.3 芯片总体结构                    | 3  |

| 4 | 产品外形图和实物图片                    | 6  |

|   | 4.1 TT335PQDS                 | 6  |

|   | 4.2 TT335PBDS                 | 7  |

| 5 | 引出端排列方式                       | 8  |

|   | 5.1 TT335PQDS 引脚排列            | 8  |

|   | 5.2 TT335PQDS 引脚描述            | 9  |

|   | 5.3 TT335PBDS 引脚排列            | 11 |

|   | 5.4 TT335PBDS 引脚描述            |    |

| 6 | 性能指标                          | 17 |

|   | 6.1 电特性                       |    |

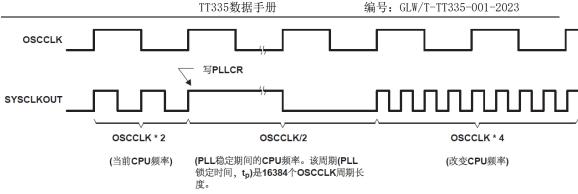

|   | 6.2 频率/周期                     | 18 |

|   | 6.3 输入输出时钟特性                  |    |

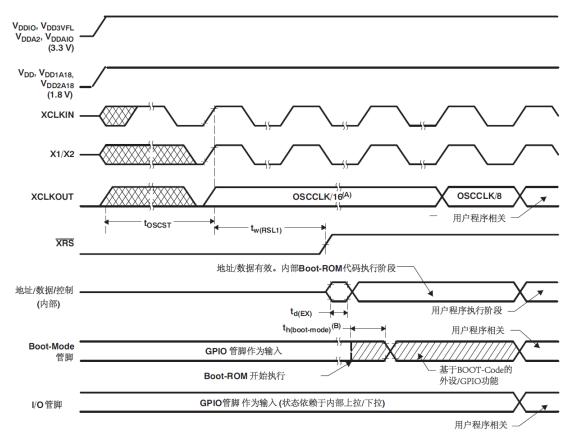

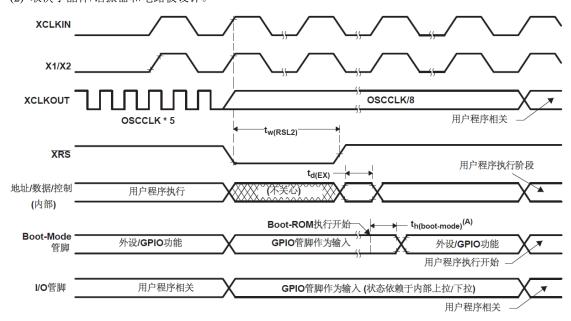

|   | 6.4 上电启动                      |    |

|   | 6.5 GPIO                      |    |

|   | 6.5.1 输出时序                    | 22 |

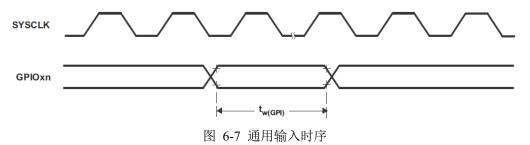

|   | 6.5.2 输入时序                    |    |

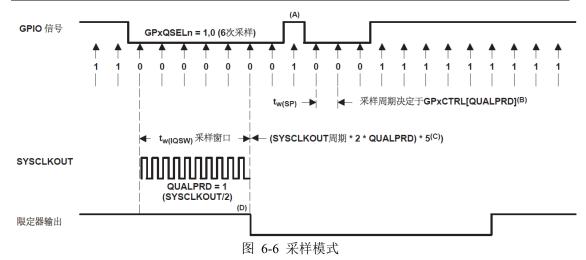

|   | 6.5.3 输入采样窗口宽度                |    |

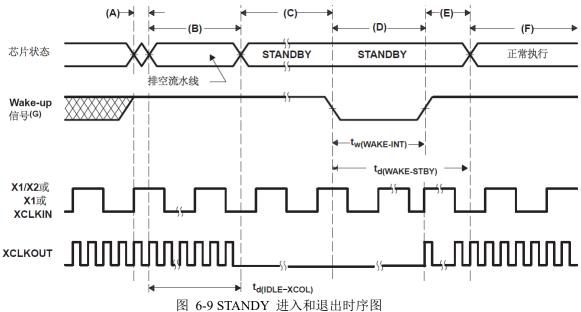

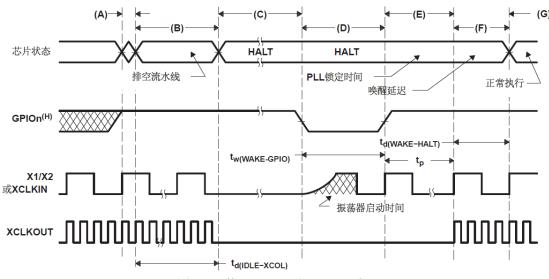

|   | 6.6 低功耗模式唤醒时序                 |    |

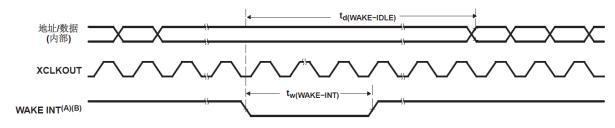

|   | 6.6.1 进入/退出 IDLE 模式           |    |

|   | 6.6.2 进入/退出 STANDBY 模式        |    |

|   | 6.6.3 进入/退出 HALT 模式           |    |

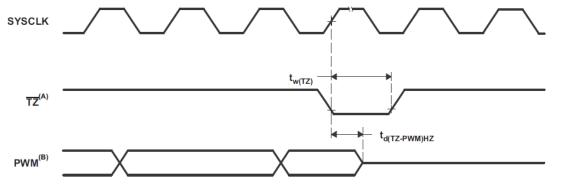

|   | 6.7 ePWM                      |    |

|   | 6.8 eCAP                      | 28 |

|   | 6.9 eQEP                      |    |

|   | 6.10 ADC                      |    |

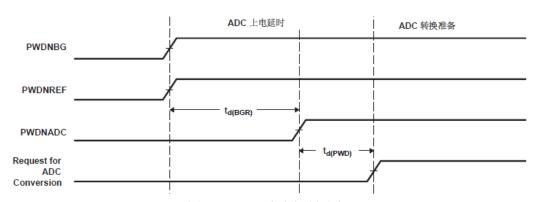

|   | 6.10.1 ADC 上电控制时序             |    |

|   | 6.10.2 定义说明                   |    |

|   | 6.10.3 顺序采样模式(单通道)(SMODE = 0) |    |

|   | 6.10.4 并发采样模式(双通道)(SMODE = 1) |    |

|   | 6.10.5 术语说明                   |    |

|   | 6.11 外部中断                     | 33 |

|   | 6.12 I2C                             | 34        |

|---|--------------------------------------|-----------|

|   | 6.13 SPI                             | 34        |

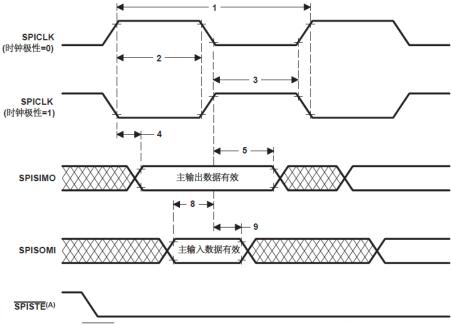

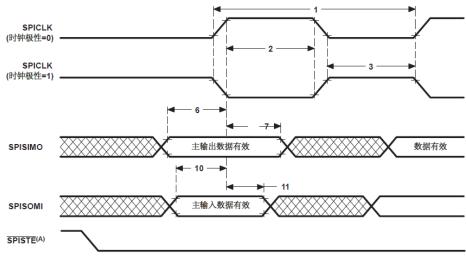

|   | 6.13.1 主模式时序                         | 34        |

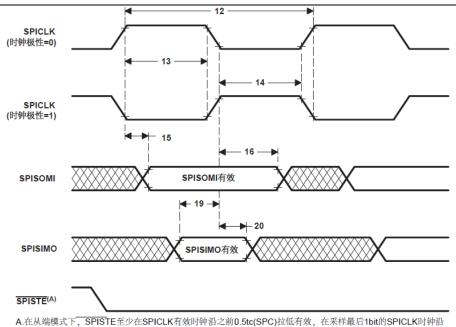

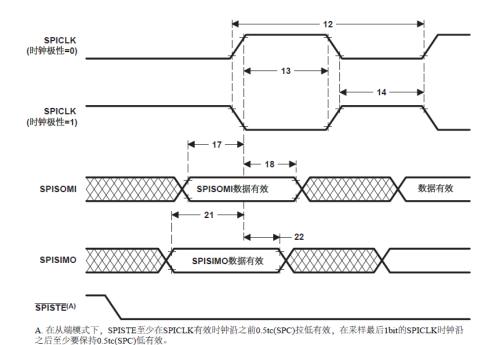

|   | 6.13.2 从模式时序                         | 40        |

|   | 6.14 McBSP                           | 42        |

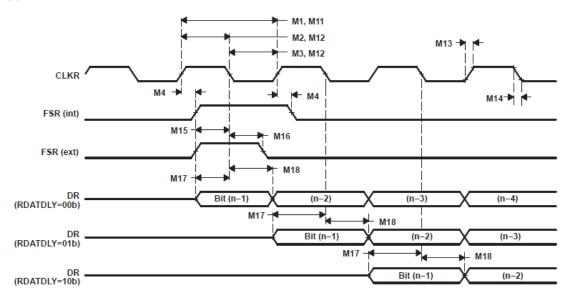

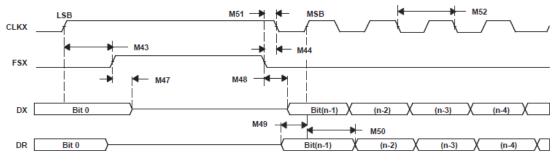

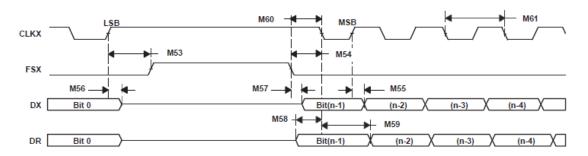

|   | 6.14.1 McBSP 发送和接收时序                 | 42        |

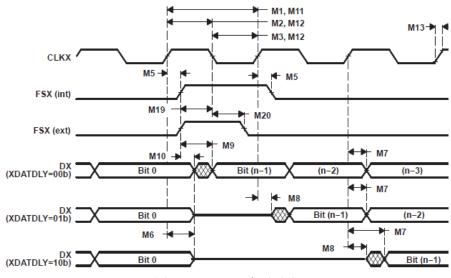

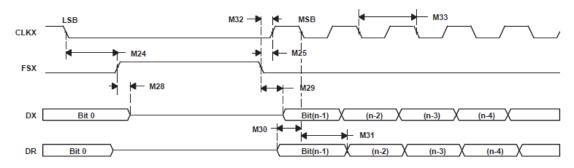

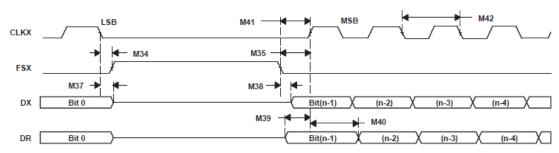

|   | 6.14.2 McBSP SPI 模式时序                | 44        |

|   | 6.15 XINTF                           | 47        |

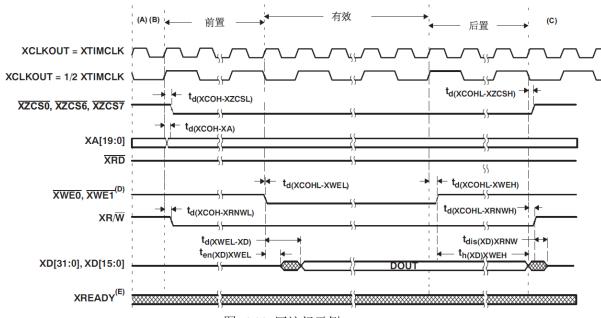

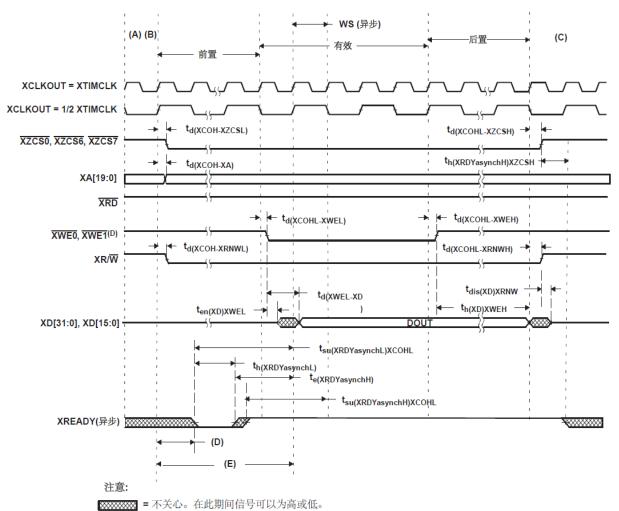

|   | 6.15.1 USEREADY = 0                  | 48        |

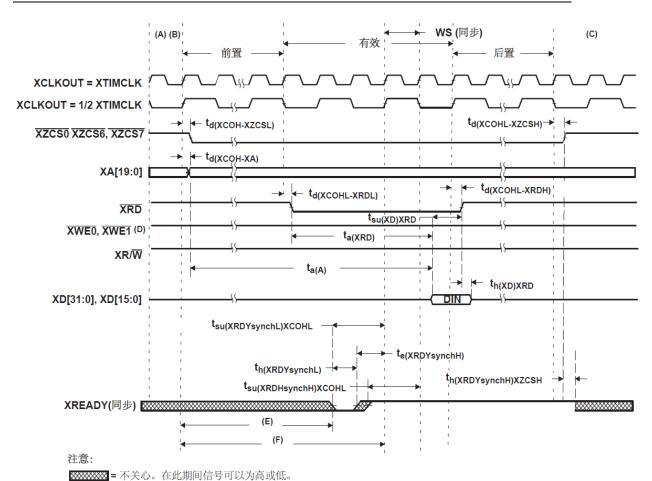

|   | 6.15.2 同步模式(USEREADY=1, READYMODE=0) | 48        |

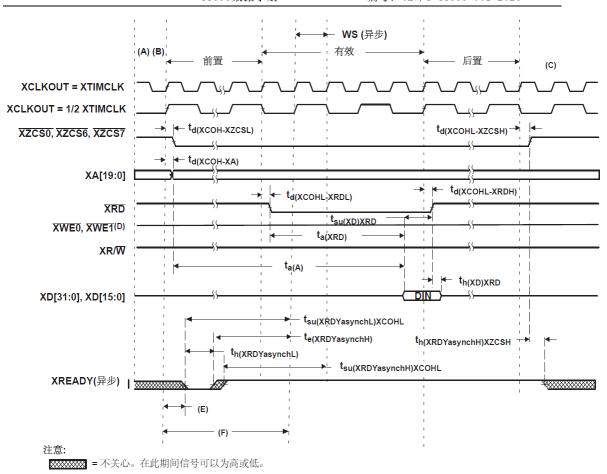

|   | 6.15.3 异步模式(USEREADY=1, READYMODE=1) | 49        |

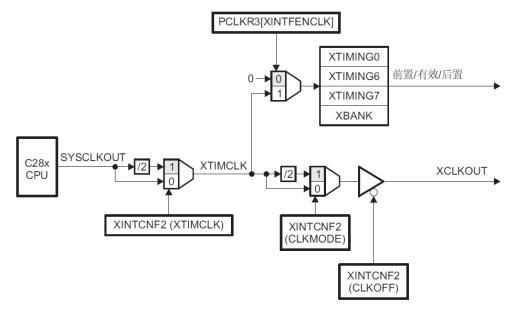

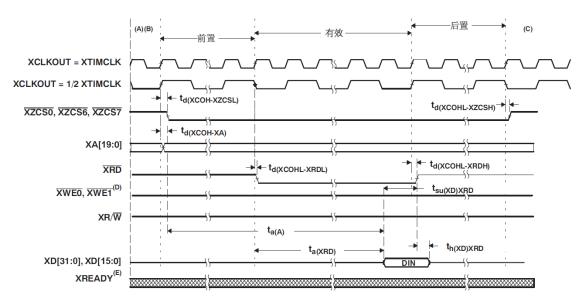

|   | 6.15.4 XINTF 信号与 XCLKOUT 的对齐关系       | 50        |

|   | 6.15.5 外部接口读取时序                      | 51        |

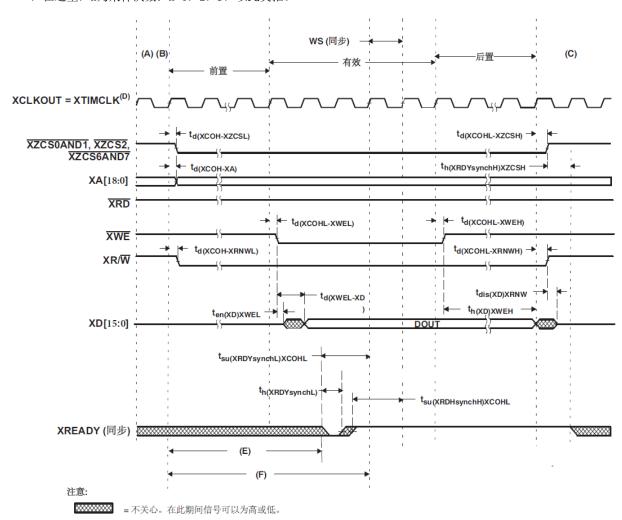

|   | 6.15.6 外部接口写入时序                      | 52        |

|   | 6.15.7 带有一个外部等待状态的外部接口读就绪时序          | 53        |

|   | 6.15.8 带有一个外部等待状态的外部接口写就绪时序          | 57        |

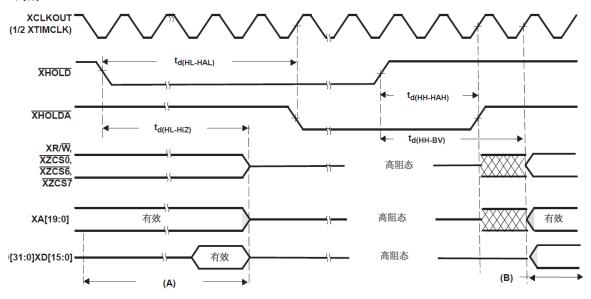

|   | 6.15.9XHOLD 和XHOLDA时序                | 60        |

|   | 6.16 Flash                           | 62        |

| 7 | 典型应用方法                               | 63        |

|   | 7.1 供电过程                             | 63        |

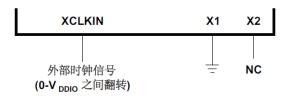

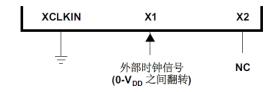

|   | 7.2 晶振的连接方法                          | 63        |

|   | 7.3 JTAG 连接                          | 63        |

|   | 7.4 ADC 连接                           | 64        |

| 8 | 使用注意事项                               | 66        |

|   | 8.1 安装注意事项                           | 66        |

|   | 8.2 产品工作条件                           | 67        |

|   | 8.2.1 电压                             | 67        |

|   | 8.2.2 电流                             | 67        |

|   | 8.2.3 时序                             | 67        |

|   | 8.2.4 Flash                          | 67        |

|   | 8.2.5 温度                             | 67        |

|   | 8.2.6 注意事项                           | 67        |

| 9 | 订货信息                                 | 68        |

|   | 9.1 型号对照表                            | 错误!未定义书签。 |

|   | 9.2 订货周期                             | 错误!未定义书签。 |

## 4 产品外形图和实物图片

TT335产品具有 LQFP176 塑封和 BGA176 塑封两种封装形式,分别命名为 TT335PQDS 和 TT335PBDS。

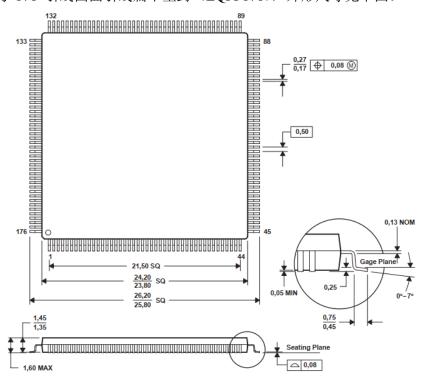

#### 4.1 TT335PQDS

该型号为 176 引线四面引线扁平塑封 (LQFP176),外形尺寸见下图。

图4-1 TT335PQDS封装外形尺寸图

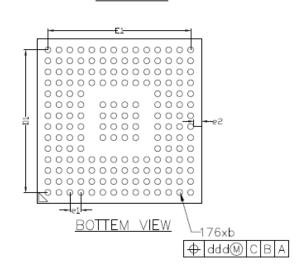

#### 4.2 TT335PBDS

该型号为 176 引线球栅阵列塑封 (BGA176),外形尺寸见下图。

| D    | imensional Ref.  |

|------|------------------|

| REF  | . Min. Nom. Max. |

| Α    | 1.02 1.06 1.1    |

| Α1   | 0.32 0.36 0.4    |

| Α2   | 0.70 BSC         |

| АЗ   | 0.4 BSC          |

| D    | 15 BSC           |

| Ε    | 15 BSC           |

| D1   | 13 BSC           |

| Ε1   | 13 BSC           |

| e1   | 1 BSC            |

| е2   | 0.74 BSC         |

| b    | 0.500 BSC        |

| Tol. | of Form&Position |

| а    | aa 0.10          |

| b    | bb 0.10          |

| d    | dd 0.05          |

图4-2 TT335PBDS外形尺寸图

## 5 引出端排列方式

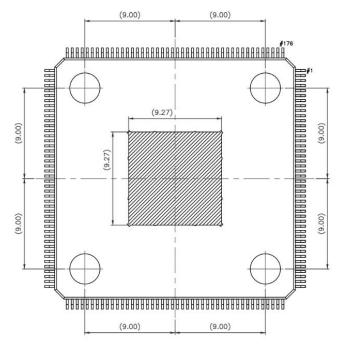

#### 5.1 TT335PQDS 引脚排列

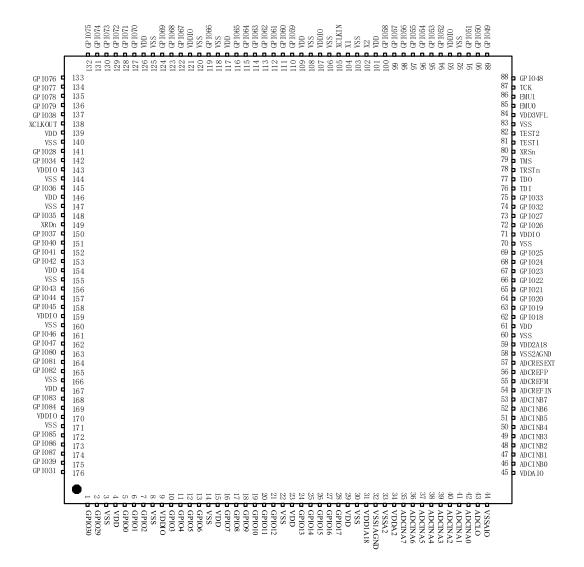

TT335PQDS 引脚排列应按下图的规定。

图5-1 TT335PQDS引脚排列

## 5.2 TT335PQDS 引脚描述

表 5-1 TT335PQDS引脚描述

| 序号 | 符号       | 类型    | 功能        | 序号  | 符号     | 类型    | 功能         |  |

|----|----------|-------|-----------|-----|--------|-------|------------|--|

| 1  | GPIO30   | I/O/Z | 通用IO端口    | 89  | GPIO49 | I/O/Z | 通用IO端口     |  |

| 2  | GPIO29   | I/O/Z | 通用IO端口    | 90  | GPIO50 | I/O/Z | 通用IO端口     |  |

| 3  | VSS      | -     | 数字地       | 91  | GPIO51 | I/O/Z | 通用IO端口     |  |

| 4  | VDD      | -     | 数字内核电源    | 92  | VSS    | -     | 数字地        |  |

| 5  | GPIO0    | I/O/Z | 通用IO端口    | 93  | VDDIO  | -     | 数字IO电源     |  |

| 6  | GPIO1    | I/O/Z | 通用IO端口    | 94  | GPIO52 | I/O/Z | 通用IO端口     |  |

| 7  | GPIO2    | I/O/Z | 通用IO端口    | 95  | GPIO53 | I/O/Z | 通用IO端口     |  |

| 8  | VSS      | -     | 数字地       | 96  | GPIO54 | I/O/Z | 通用IO端口     |  |

| 9  | VDDIO    | -     | 数字IO电源    | 97  | GPIO55 | I/O/Z | 通用IO端口     |  |

| 10 | GPIO3    | I/O/Z | 通用IO端口    | 98  | GPIO56 | I/O/Z | 通用IO端口     |  |

| 11 | GPIO4    | I/O/Z | 通用IO端口    | 99  | GPIO57 | I/O/Z | 通用IO端口     |  |

| 12 | GPIO5    | I/O/Z | 通用IO端口    | 100 | GPIO58 | I/O/Z | 通用IO端口     |  |

| 13 | GPIO6    | I/O/Z | 通用IO端口    | 101 | VDD    | -     | 数字内核电源     |  |

| 14 | VSS      | -     | 数字地       | 102 | X2     | 0     | 内部振荡器输出    |  |

| 15 | VDD      | -     | 数字内核电源    | 103 | VSS    | -     | 数字地        |  |

| 16 | GPIO7    | I/O/Z | 通用IO端口    | 104 | X1     | I     | 内部/外部振荡器输入 |  |

| 17 | GPIO8    | I/O/Z | 通用IO端口    | 105 | XCLKIN | I     | 外部振荡器输入    |  |

| 18 | GPIO9    | I/O/Z | 通用IO端口    | 106 | VSS    | -     | 数字地        |  |

| 19 | GPIO10   | I/O/Z | 通用IO端口    | 107 | VDDIO  | -     | 数字IO电源     |  |

| 20 | GPIO11   | I/O/Z | 通用IO端口    | 108 | VSS    | -     | 数字地        |  |

| 21 | GPIO12   | I/O/Z | 通用IO端口    | 109 | VDD    | -     | 数字内核电源     |  |

| 22 | VSS      | -     | 数字地       | 110 | GPIO59 | I/O/Z | 通用IO端口     |  |

| 23 | VDD      | -     | 数字内核电源    | 111 | GPIO60 | I/O/Z | 通用IO端口     |  |

| 24 | GPIO13   | I/O/Z | 通用IO端口    | 112 | GPIO61 | I/O/Z | 通用IO端口     |  |

| 25 | GPIO14   | I/O/Z | 通用IO端口    | 113 | GPIO62 | I/O/Z | 通用IO端口     |  |

| 26 | GPIO15   | I/O/Z | 通用IO端口    | 114 | GPIO63 | I/O/Z | 通用IO端口     |  |

| 27 | GPIO16   | I/O/Z | 通用IO端口    | 115 | GPIO64 | I/O/Z | 通用IO端口     |  |

| 28 | GPIO17   | I/O/Z | 通用IO端口    | 116 | GPIO65 | I/O/Z | 通用IO端口     |  |

| 29 | VDD      | -     | 数字内核电源    | 117 | VDD    | -     | 数字内核电源     |  |

| 30 | VSS      | -     | 数字地       | 118 | VSS    | -     | 数字地        |  |

| 31 | VDD1A18  | -     | ADC内核电源   | 119 | GPIO66 | I/O/Z | 通用IO端口     |  |

| 32 | VSS1AGND | -     | ADC内核地    | 120 | VSS    | -     | 数字地        |  |

| 33 | VSSA2    | -     | ADC内核地    | 121 | VDDIO  | -     | 数字IO电源     |  |

| 34 | VDDA2    | -     | ADC内核电源   | 122 | GPIO67 | I/O/Z | 通用IO端口     |  |

| 35 | ADCINA7  | I     | ADC模拟通道输入 | 123 | GPIO68 | I/O/Z | 通用IO端口     |  |

| 36 | ADCINA6  | I     | ADC模拟通道输入 | 124 | GPIO69 | I/O/Z | 通用IO端口     |  |

| 37 | ADCINA5  | I     | ADC模拟通道输入 | 125 | VSS    | -     | 数字地        |  |

| 38 | ADCINA4  | I     | ADC模拟通道输入 | 126 | VDD    | -     | 数字内核电源     |  |

| 39 | ADCINA3  | I     | ADC模拟通道输入 | 127 | GPIO70 | I/O/Z | 通用IO端口     |  |

表 5-1TT335PQDS 引脚描述 (续)

| 序号 | 符号        | 类型    | 功能          | 序号  | 符号      | 类型    | 功能     |

|----|-----------|-------|-------------|-----|---------|-------|--------|

| 40 | ADCINA2   | 1     | ADC模拟通道输入   | 128 | GPIO71  | I/O/Z | 通用IO端口 |

| 41 | ADCINA1   | I     | ADC模拟通道输入   | 129 | GPIO72  | I/O/Z | 通用IO端口 |

| 42 | ADCINA0   | I     | ADC模拟通道输入   | 130 | GPIO73  | I/O/Z | 通用IO端口 |

| 43 | ADCLO     | -     | ADC内核地      | 131 | GPIO74  | I/O/Z | 通用IO端口 |

| 44 | VSSAIO    | -     | ADCIO地      | 132 | GPIO75  | I/O/Z | 通用IO端口 |

| 45 | VDDAIO    | -     | ADCIO电源     | 133 | GPIO76  | I/O/Z | 通用IO端口 |

| 46 | ADCINB0   | I     | ADC模拟通道输入   | 134 | GPIO77  | I/O/Z | 通用IO端口 |

| 47 | ADCINB1   | I     | ADC模拟通道输入   | 135 | GPIO78  | I/O/Z | 通用IO端口 |

| 48 | ADCINB2   | I     | ADC模拟通道输入   | 136 | GPIO79  | I/O/Z | 通用IO端口 |

| 49 | ADCINB3   | I     | ADC模拟通道输入   | 137 | GPIO38  | I/O/Z | 通用IO端口 |

| 50 | ADCINB4   | I     | ADC模拟通道输入   | 138 | XCLKOUT | O/Z   | 系统时钟输出 |

| 51 | ADCINB5   | 1     | ADC模拟通道输入   | 139 | VDD     | -     | 数字内核电源 |

| 52 | ADCINB6   | 1     | ADC模拟通道输入   | 140 | VSS     | -     | 数字地    |

| 53 | ADCINB7   | 1     | ADC模拟通道输入   | 141 | GPIO28  | I/O/Z | 通用IO端口 |

| 54 | ADCREFIN  | 1     | ADC外部参考输入   | 142 | GPIO34  | I/O/Z | 通用IO端口 |

| 55 | ADCREFM   | 0     | ADC内部参考输出   | 143 | VDDIO   | -     | 数字IO电源 |

| 56 | ADCREFP   | 0     | ADC内部参考输出   | 144 | VSS     | -     | 数字地    |

| 57 | ADCRESEXT | 1     | ADC外部电流偏置电阻 | 145 | GPIO36  | I/O/Z | 通用IO端口 |

| 58 | VSS2AGND  | -     | ADC内核地      | 146 | VDD     | -     | 数字内核电源 |

| 59 | VDD2A18   | -     | ADC内核电源     | 147 | VSS     | -     | 数字地    |

| 60 | VSS       | -     | 数字地         | 148 | GPIO35  | I/O/Z | 通用IO端口 |

| 61 | VDD       | -     | 数字内核电源      | 149 | XRDn    | O/Z   | 外部读使能  |

| 62 | GPIO18    | I/O/Z | 通用IO端口      | 150 | GPIO37  | I/O/Z | 通用IO端口 |

| 63 | GPIO19    | I/O/Z | 通用IO端口      | 151 | GPIO40  | I/O/Z | 通用IO端口 |

| 64 | GPIO20    | I/O/Z | 通用IO端口      | 152 | GPIO41  | I/O/Z | 通用IO端口 |

| 65 | GPIO21    | I/O/Z | 通用IO端口      | 153 | GPIO42  | I/O/Z | 通用IO端口 |

| 66 | GPIO22    | I/O/Z | 通用IO端口      | 154 | VDD     | -     | 数字内核电源 |

| 67 | GPIO23    | I/O/Z | 通用IO端口      | 155 | VSS     | -     | 数字地    |

| 68 | GPIO24    | I/O/Z | 通用IO端口      | 156 | GPIO43  | I/O/Z | 通用IO端口 |

| 69 | GPIO25    | I/O/Z | 通用IO端口      | 157 | GPIO44  | I/O/Z | 通用IO端口 |

| 70 | VSS       | -     | 数字地         | 158 | GPIO45  | I/O/Z | 通用IO端口 |

| 71 | VDDIO     | -     | 数字IO电源      | 159 | VDDIO   | -     | 数字IO电源 |

| 72 | GPIO26    | I/O/Z | 通用IO端口      | 160 | VSS     | -     | 数字地    |

| 73 | GPIO27    | I/O/Z | 通用IO端口      | 161 | GPIO46  | I/O/Z | 通用IO端口 |

| 74 | GPIO32    | I/O/Z | 通用IO端口      | 162 | GPIO47  | I/O/Z | 通用IO端口 |

| 75 | GPIO33    | I/O/Z | 通用IO端口      | 163 | GPIO80  | I/O/Z | 通用IO端口 |

| 76 | TDI       | I     | JTAG测试数据输入  | 164 | GPIO81  | I/O/Z | 通用IO端口 |

| 77 | TDO       | O/Z   | JTAG测试数据输出  | 165 | GPIO82  | I/O/Z | 通用IO端口 |

| 78 | TRST      |       | JTAG测试复位    | 166 | VSS     | -     | 数字地    |

| 79 | TMS       | 1     | JTAG测试模式选择  | 167 | VDD     | -     |        |

表 5-1 TT335PQDS 引脚(续)

| 序号 | 符号      | 类型    | 功能          | 序号  | 符号     | 类型    | 功能     |

|----|---------|-------|-------------|-----|--------|-------|--------|

| 80 | XRS     | I/OD  | 复位 (开漏)     | 168 | GPIO83 | I/O/Z | 通用IO端口 |

| 81 | TEST1   | 1/0   | 测试引脚,必须悬空   | 169 | GPIO84 | I/O/Z | 通用IO端口 |

| 82 | TEST2   | 1/0   | 测试引脚,必须悬空   | 170 | VDDIO  | -     | 数字IO电源 |

| 83 | VSS     | -     | 数字地         | 171 | VSS    | -     | 数字地    |

| 84 | VDD3VFL | -     | 3.3VFLASH电源 | 172 | GPIO85 | I/O/Z | 通用IO端口 |

| 85 | EMU0    | I/O/Z | 仿真端口        | 173 | GPIO86 | I/O/Z | 通用IO端口 |

| 86 | EMU1    | I/O/Z | 仿真端口        | 174 | GPIO87 | I/O/Z | 通用IO端口 |

| 87 | TCK     | 1     | JTAG测试时钟    | 175 | GPIO39 | I/O/Z | 通用IO端口 |

| 88 | GPIO48  | I/O/Z | 通用IO端口      | 176 | GPIO31 | I/O/Z | 通用IO端口 |

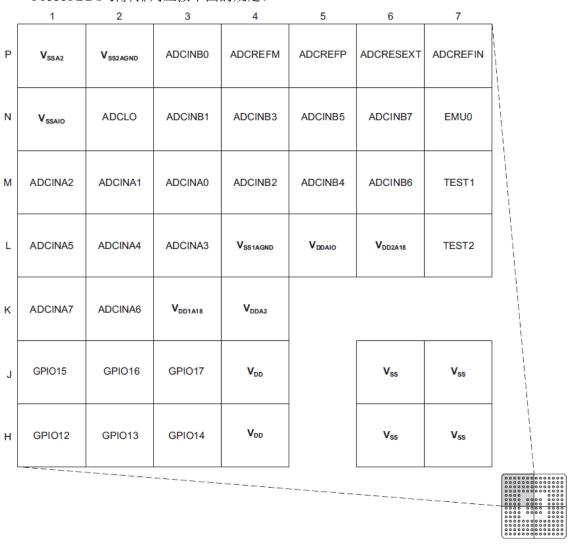

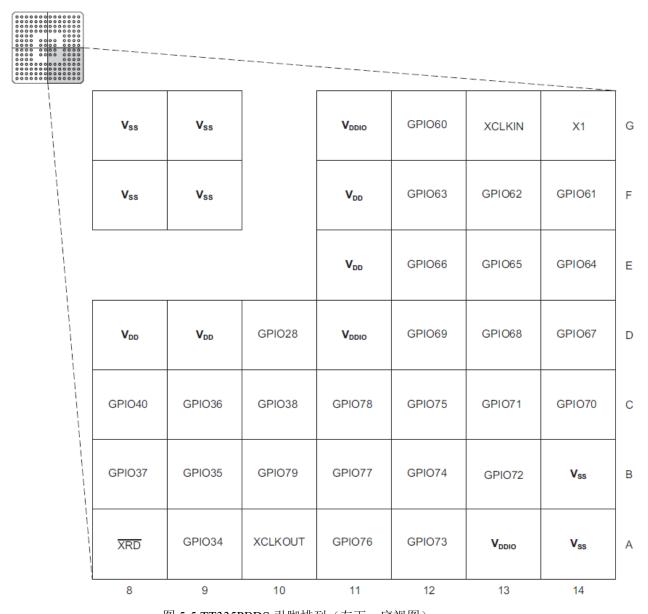

## 5.3 TT335PBDS 引脚排列

TT335PBDS 引脚排列应按下图的规定。

图5-2 TT335PBDS引脚排列(左上,底视图)

服务电话:008618924645428 008617302669239

|  | 8               | 9                   | 10                | 11              | 12     | 13              | 14                | 1 |

|--|-----------------|---------------------|-------------------|-----------------|--------|-----------------|-------------------|---|

|  | EMU1            | GPIO20              | GPIO23            | GPIO26          | GPIO33 | V <sub>ss</sub> | V <sub>ss</sub>   | Р |

|  | GPIO18          | GPIO21              | GPIO24            | GPIO27          | TDI    | TDO             | V <sub>DDIO</sub> | N |

|  | GPIO19          | GPIO22              | GPIO25            | GPIO32          | TMS    | XRS             | тск               | М |

|  | V <sub>DD</sub> | V <sub>DD3VFL</sub> | V <sub>DDIO</sub> | TRST            | GPIO50 | GPIO49          | GPIO48            | L |

|  |                 |                     |                   | V <sub>DD</sub> | GPIO53 | GPIO52          | GPIO51            | K |

|  | V <sub>ss</sub> | V <sub>ss</sub>     |                   | V <sub>DD</sub> | GPIO56 | GPIO55          | GPIO54            | J |

|  | V <sub>ss</sub> | V <sub>ss</sub>     |                   | GPIO59          | GPIO58 | GPIO57          | X2                | н |

|  |                 |                     |                   |                 |        |                 |                   |   |

图5-3 TT335PBDS引脚排列(右上,底视图)

| G | GPIO9             | GPIO10          | GPIO11 | V <sub>DDIO</sub>      |                 | V <sub>ss</sub> | V <sub>ss</sub>   |   |

|---|-------------------|-----------------|--------|------------------------|-----------------|-----------------|-------------------|---|

| F | GPIO6             | GPI07           | GPIO8  | <b>V</b> <sub>DD</sub> |                 | V <sub>ss</sub> | V <sub>ss</sub>   |   |

| E | GPIO3             | GPIO4           | GPIO5  | V <sub>DDIO</sub>      |                 |                 |                   |   |

| D | GPIO0             | GPIO1           | GPIO2  | V <sub>DD</sub>        | V <sub>DD</sub> | GPIO47          | V <sub>DDIO</sub> |   |

| С | GPIO29            | GPIO30          | GPIO39 | GPIO85                 | GPIO82          | GPIO46          | GPIO43            |   |

| В | V <sub>DDIO</sub> | GPIO31          | GPIO87 | GPIO84                 | GPIO81          | GPIO45          | GPIO42            |   |

| Α | V <sub>ss</sub>   | V <sub>ss</sub> | GPIO86 | GPIO83                 | GPIO80          | GPIO44          | GPIO41            |   |

| l | 1                 | 2               | 3      | 4                      | 5               | 6               | 7                 | J |

图5-4 TT335PBDS引脚排列(左上,底视图)

图 5-5 TT335PBDS 引脚排列 (左下,底视图)

## 5.4 TT335PBDS 引脚描述

表 5-2 TT335PBDS引脚描述

| 序号  | 符号      | 类型    | 功能     | 序号  | 符号     | 类型    | 功能     |

|-----|---------|-------|--------|-----|--------|-------|--------|

| A1  | VSS     | -     | 数字地    | C12 | GPIO75 | I/O/Z | 通用IO端口 |

| A2  | VSS     | -     | 数字地    | C13 | GPIO71 | I/O/Z | 通用IO端口 |

| А3  | GPIO86  | I/O/Z | 通用IO端口 | C14 | GPIO70 | I/O/Z | 通用IO端口 |

| A4  | GPIO83  | I/O/Z | 通用IO端口 | D1  | GPIO0  | I/O/Z | 通用IO端口 |

| A5  | GPIO80  | I/O/Z | 通用IO端口 | D2  | GPIO1  | I/O/Z | 通用IO端口 |

| A6  | GPIO44  | I/O/Z | 通用IO端口 | D3  | GPIO2  | I/O/Z | 通用IO端口 |

| A7  | GPIO41  | I/O/Z | 通用IO端口 | D4  | VDD    | -     | 数字内核电源 |

| A8  | XRDn    | O/Z   | 外部读使能  | D5  | VDD    | -     | 数字内核电源 |

| A9  | GPIO34  | I/O/Z | 通用IO端口 | D6  | GPIO47 | I/O/Z | 通用IO端口 |

| A10 | XCLKOUT | O/Z   | 系统时钟输出 | D7  | VDDIO  | -     | 数字IO电源 |

| A11 | GPIO76  | I/O/Z | 通用IO端口 | D8  | VDD    | -     | 数字内核电源 |

| A12 | GPIO73  | I/O/Z | 通用IO端口 | D9  | VDD    | -     | 数字内核电源 |

| A13 | VDDIO   | -     | 数字IO电源 | D10 | GPIO28 | I/O/Z | 通用IO端口 |

| A14 | VSS     | -     | 数字地    | D11 | VDDIO  | -     | 数字IO电源 |

| B1  | VDDIO   | -     | 数字IO电源 | D12 | GPIO69 | I/O/Z | 通用IO端口 |

| B2  | GPIO31  | I/O/Z | 通用IO端口 | D13 | GPIO68 | I/O/Z | 通用IO端口 |

| В3  | GPIO87  | I/O/Z | 通用IO端口 | D14 | GPIO67 | I/O/Z | 通用IO端口 |

| B4  | GPIO84  | I/O/Z | 通用IO端口 | E1  | GPIO3  | I/O/Z | 通用IO端口 |

| B5  | GPIO81  | I/O/Z | 通用IO端口 | E2  | GPIO4  | I/O/Z | 通用IO端口 |

| В6  | GPIO45  | I/O/Z | 通用IO端口 | E3  | GPIO6  | I/O/Z | 通用IO端口 |

| В7  | GPIO42  | I/O/Z | 通用IO端口 | E4  | VDDIO  | -     | 数字IO电源 |

| B8  | GPIO37  | I/O/Z | 通用IO端口 | E11 | VDD    | -     | 数字内核电源 |

| В9  | GPIO35  | I/O/Z | 通用IO端口 | E12 | GPIO66 | I/O/Z | 通用IO端口 |

| B10 | GPIO79  | I/O/Z | 通用IO端口 | E13 | GPIO65 | I/O/Z | 通用IO端口 |

| B11 | GPIO77  | I/O/Z | 通用IO端口 | E14 | GPIO64 | I/O/Z | 通用IO端口 |

| B12 | GPIO74  | I/O/Z | 通用IO端口 | F1  | GPIO6  | I/O/Z | 通用IO端口 |

| B13 | GPIO72  | I/O/Z | 通用IO端口 | F2  | GPIO7  | I/O/Z | 通用IO端口 |

| B14 | VSS     | -     | 数字地    | F3  | GPIO8  | I/O/Z | 通用IO端口 |

| C1  | GPIO29  | I/O/Z | 通用IO端口 | F4  | VDD    | -     | 数字内核电源 |

| C2  | GPIO30  | I/O/Z | 通用IO端口 | F6  | VSS    | -     | 数字地    |

| C3  | GPIO39  | I/O/Z | 通用IO端口 | F7  | VSS    | -     | 数字地    |

| C4  | GPIO85  | I/O/Z | 通用IO端口 | F8  | VSS    | -     | 数字地    |

| C5  | GPIO82  | I/O/Z | 通用IO端口 | F9  | VSS    | -     | 数字地    |

| C6  | GPIO46  | I/O/Z | 通用IO端口 | F11 | VDD    | -     | 数字内核电源 |

| C7  | GPIO43  | I/O/Z | 通用IO端口 | F12 | GPIO63 | I/O/Z | 通用IO端口 |

| C8  | GPIO40  | I/O/Z | 通用IO端口 | F13 | GPIO62 | I/O/Z | 通用IO端口 |

| С9  | GPIO36  | I/O/Z | 通用IO端口 | F14 | GPIO61 | I/O/Z | 通用IO端口 |

| C10 | GPIO38  | I/O/Z | 通用IO端口 | G1  | GPIO9  | I/O/Z | 通用IO端口 |

| C11 | GPIO78  | I/O/Z | 通用IO端口 | G2  | GPIO10 | I/O/Z | 通用IO端口 |

15

表 5-2 TT335PBDS 引脚描述(续)

| 序号  | 符号      | 类型    | 衣 3-2 11333P<br>功能 | 序号  | 符号       | 类型    |             |

|-----|---------|-------|--------------------|-----|----------|-------|-------------|

| G3  | GPIO11  | I/O/Z | 通用IO端口             | K12 | GPIO53   | I/O/Z |             |

| G4  | VDDIO   | -     | 数字IO电源             | K13 | GPIO52   | I/O/Z | 通用IO端口      |

| G6  | VSS     | -     |                    | K14 | GPIO51   | I/O/Z |             |

| G7  | VSS     | -     |                    | L1  | ADCINA5  | ı     | ADC模拟通道输入   |

| G8  | VSS     | -     |                    | L2  | ADCINA4  | 1     | ADC模拟通道输入   |

| G9  | VSS     | -     | 数字地                | L3  | ADCINA3  | 1     | ADC模拟通道输入   |

| G11 | VDDIO   | -     | 数字IO电源             | L4  | VSS1AGND | -     | ADC内核地      |

| G12 | GPIO60  | I/O/Z | 通用IO端口             | L5  | VSSAIO   | -     | ADCIO地      |

| G13 | XCLKIN  | I     | 外部振荡器输入            | L6  | VDD2A18  | -     | ADC内核电源     |

| G14 | X1      | I     | 内部/外部振荡器输入         | L7  | TEST2    | 1/0   | 测试引脚, 必须悬空  |

| H1  | GPIO12  | I/O/Z | 通用IO端口             | L8  | VDD      | -     | 数字内核电源      |

| H2  | GPIO13  | I/O/Z | 通用IO端口             | L9  | VDD3VFL  | -     | 3.3VFLASH电源 |

| НЗ  | GPIO14  | I/O/Z | 通用IO端口             | L10 | VDDIO    | -     | 数字IO电源      |

| H4  | VDD     | -     | 数字内核电源             | L11 | TRST     |       | JTAG测试复位    |

| Н6  | VSS     | -     | 数字地                | L12 | GPIO50   | I/O/Z | 通用IO端口      |

| H7  | VSS     | -     | 数字地                | L13 | GPIO49   | I/O/Z | 通用IO端口      |

| Н8  | VSS     | -     | 数字地                | L14 | GPIO48   | I/O/Z | 通用IO端口      |

| Н9  | VSS     | -     | 数字地                | M1  | ADCINA2  | I     | ADC模拟通道输入   |

| H11 | GPIO59  | I/O/Z | 通用IO端口             | M2  | ADCINA1  | I     | ADC模拟通道输入   |

| H12 | GPIO58  | I/O/Z | 通用IO端口             | M3  | ADCINA0  | I     | ADC模拟通道输入   |

| H13 | GPIO57  | I/O/Z | 通用IO端口             | M4  | ADCINB2  | I     | ADC模拟通道输入   |

| H14 | X2      | 0     | 内部振荡器输出            | M5  | ADCINB4  | I     | ADC模拟通道输入   |

| J1  | GPIO15  | I/O/Z | 通用IO端口             | M6  | ADCINB6  | I     | ADC模拟通道输入   |

| J2  | GPIO16  | I/O/Z | 通用IO端口             | M7  | TEST1    | 1/0   | 测试引脚, 必须悬空  |

| J3  | GPIO17  | I/O/Z | 通用IO端口             | M8  | GPIO19   | I/O/Z | 通用IO端口      |

| J4  | VDD     | -     | 数字内核电源             | M9  | GPIO22   | I/O/Z | 通用IO端口      |

| Ј6  | VSS     | -     | 数字地                | M10 | GPIO25   | I/O/Z | 通用IO端口      |

| J7  | VSS     | -     | 数字地                | M11 | GPIO32   | I/O/Z | 通用IO端口      |

| Ј8  | VSS     | -     | 数字地                | M12 | TMS      | 1     | JTAG测试模式选择  |

| J9  | VSS     | -     | 数字地                | M13 | XRS      | I/OD  | 复位 (开漏)     |

| J11 | VDD     | -     | 数字内核电源             | M14 | TCK      | I     | JTAG测试时钟    |

| J12 | GPIO56  | I/O/Z | 通用IO端口             | N1  | VSSAIO   | -     | ADCIO地      |

| J13 | GPIO55  | I/O/Z | 通用IO端口             | N2  | ADCLO    | -     | ADC内核地      |

| J14 | GPIO54  | I/O/Z | 通用IO端口             | N3  | ADCINB1  | 1     | ADC模拟通道输入   |

| K1  | ADCINA7 | I     | ADC模拟通道输入          | N4  | ADCINB3  | 1     | ADC模拟通道输入   |

| K2  | ADCINA6 | I     | ADC模拟通道输入          | N5  | ADCINB5  | ı     | ADC模拟通道输入   |

| K3  | VDD1A18 | -     | ADC内核电源            | N6  | ADCINB7  | I     | ADC模拟通道输入   |

| K4  | VDDA2   | -     | ADC内核电源            | N7  | EMU0     | I/O/Z | 仿真端口        |

| K11 | VDD     | -     | 数字内核电源             | N8  | GPIO18   | I/O/Z | 通用IO端口      |

表 5-2 TT335PBDS 引脚描述 (续)

| 序号  | 符号       | 类型    | 功能         | 序号  | 符号        | 类型    | 功能          |

|-----|----------|-------|------------|-----|-----------|-------|-------------|

| N9  | GPIO21   | I/O/Z | 通用IO端口     | P5  | ADCREFP   | 0     | ADC内部参考输出   |

| N10 | GPIO24   | I/O/Z | 通用IO端口     | P6  | ADCRESEXT | 1     | ADC外部电流偏置电阻 |

| N11 | GPIO27   | I/O/Z | 通用IO端口     | P7  | ADCREFIN  | 1     | ADC外部参考输入   |

| N12 | TDI      | 1     | JTAG测试数据输入 | P8  | EMU1      | I/O/Z | 仿真端口        |

| N13 | TDO      | O/Z   | JTAG测试数据输出 | P9  | GPIO20    | I/O/Z | 通用IO端口      |

| N14 | VDDIO    | -     | 数字IO电源     | P10 | GPIO23    | I/O/Z | 通用IO端口      |

| P1  | VSSA2    | -     | ADC内核地     | P11 | GPIO26    | I/O/Z | 通用IO端口      |

| P2  | VSS2AGND | -     | ADC内核地     | P12 | GPIO33    | I/O/Z | 通用IO端口      |

| Р3  | ADCINB0  | I     | ADC模拟通道输入  | P13 | VSS       | -     | 数字地         |

| P4  | ADCREFM  | 0     | ADC内部参考输出  | P14 | VSS       | -     | 数字地         |

# 6 性能指标

## 6.1 电特性

除另有规定,电特性应符合下表规定,并适用于全温度范围。

表 6-1 电特性

| 特性                                     | 符号                   | 测试条件c<br>除另有规定,-55℃≤TA≤12                                                                                                                     | 25°C,                  | 极限                  | 值     | 单位 |  |

|----------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------------------|-------|----|--|

| 行任                                     | 1) 5                 | V <sub>DDA2</sub> , V <sub>DDAI0</sub> , V <sub>DDI0</sub> , V <sub>DD</sub><br>V <sub>DDIA18</sub> , V <sub>DD2A18</sub> , V <sub>DD</sub> = |                        | 最小                  | 最大    | 平位 |  |

| 输出低电平电压                                | $V_{OL}$             | I <sub>OL</sub> =4mA                                                                                                                          |                        | _                   | 0.4   | V  |  |

| <b>输出高电平电压</b>                         | $V_{OH}$             | V <sub>DDIO</sub> =3.135V, I <sub>OH</sub> =-4mA                                                                                              |                        | 2.4                 | _     |    |  |

| 柳田同屯「屯压                                | * OH                 | V <sub>DDIO</sub> =3.135V, I <sub>OH</sub> =50μA                                                                                              |                        | $V_{\rm DDIO}$ -0.2 |       | V  |  |

| 输入低电平漏电流 <sup>a</sup>                  | ${ m I}_{ m IL}$     | 上拉, V <sub>DDIO</sub> =3.3V, V <sub>IN</sub> =0V, 所有IO                                                                                        | Os (含 <del>XRS</del> ) | -44.6               | -97.2 |    |  |

|                                        | IL                   | 下拉, V <sub>DDIO</sub> =3.3V, V <sub>IN</sub> =0V                                                                                              |                        | -5                  | 5     | μA |  |

| 输入高电平漏电流 <sup>a</sup> I <sub>III</sub> |                      | 上拉, V <sub>DDIO</sub> =3.3V, V <sub>IN</sub> =V <sub>DDIO</sub>                                                                               |                        | -5                  | 5     |    |  |

| 柳八同里上烟里加                               | *IH                  | 下拉, V <sub>DDIO</sub> =3.3V, V <sub>IN</sub> =V <sub>DDIO</sub>                                                                               | 38.4                   | 113.8               | μΑ    |    |  |

| 输出高阻时引脚电流 <sup>a</sup>                 | $I_{OZ}$             | V <sub>DDIO</sub> =3.465V,V <sub>O</sub> =V <sub>DDIO</sub> 或0V                                                                               | -5                     | 5                   | μA    |    |  |

| 输入电容 <sup>b</sup>                      | $C_{\rm I}$          | T <sub>A</sub> =25°C                                                                                                                          |                        | _                   | 25.0  | pF |  |

|                                        |                      | N V V V 2465V                                                                                                                                 | 工作模式                   |                     | 395   | mA |  |

|                                        |                      | $V_{DDA2}$ , $V_{DDAIO}$ , $V_{DDIO}$ , $V_{DD3VFL}$ =3.465V                                                                                  | IDLE模式                 |                     | 200   | mA |  |

|                                        | $I_{DD}d$            | $V_{DD1A18}, V_{DD2A18}, V_{DD}=1.8V;$                                                                                                        | STANDBY模式              |                     | 15    | mA |  |

|                                        |                      |                                                                                                                                               | HALT模式                 | _                   | 5     | mA |  |

|                                        |                      | $V_{SSA2}$ , $V_{SSAIO}$ , $V_{SS1AGND}$ , $V_{SS2AGND}$ ,                                                                                    | 工作模式                   |                     | 90    | mA |  |

|                                        |                      | $V_{SS}=0V;$                                                                                                                                  | IDLE模式                 |                     | 700   | μA |  |

|                                        | $I_{DDIO}$           | 工作模式和IDLE模式时                                                                                                                                  | STANDBY模式              | _                   | 700   | μA |  |

|                                        |                      | fsysclkout=150MHz;                                                                                                                            | HALT模式                 | _                   | 300   | μA |  |

|                                        |                      | STANDBY模式和HALT <sup>e</sup> 模式时                                                                                                               | 工作模式                   | _                   | 35    | mA |  |

|                                        | $I_{\mathrm{DDA18}}$ | fsysclkout=0Hz。                                                                                                                               | IDLE模式                 |                     | 60    | μA |  |

|                                        |                      | yordendor orang                                                                                                                               | STANDBY模式              | _                   | 60    | μA |  |

17

服务电话:008618924645428 008617302669239

|      |             |                                                                                       | HALT模式       | _ | 60 | μA |  |

|------|-------------|---------------------------------------------------------------------------------------|--------------|---|----|----|--|

|      |             |                                                                                       | 工作模式         | _ | 2  | mA |  |

|      |             |                                                                                       | IDLE模式       | _ | 50 | μA |  |

|      | $I_{DDA33}$ |                                                                                       | STANDBY模式    | _ | 50 | μA |  |

|      |             |                                                                                       | HALT模式       | _ | 50 | μA |  |

|      |             | V <sub>DDA2</sub> , V <sub>DDAIO</sub> , V <sub>DDIO</sub> , V <sub>DD3VFL</sub> =3.1 | .35V~3.465V; |   |    |    |  |

| 功能测试 |             | V <sub>DD1A18</sub> , V <sub>DD2A18</sub> , V <sub>DD</sub> =1.71V~1.89               | V;           |   |    |    |  |

|      |             | $V_{SSA2}$ , $V_{SSAIO}$ , $V_{SS1AGND}$ , $V_{SS2AGND}$                              | $V_{SS}=0V$  |   |    |    |  |

注电压均以Vss为基准, Vss=0V。电流以流入器件引出端为正。

c测试条件: (1) 工作模式: ePWM1~6、eCAP1~6、eQEP1~2、eCAN-A、SCI-A(FIFO模式》SCI-B(FIFO模式》SPI-A(FIFO模式》ADC、I2C、CPU-Timer1/2/3等外设时钟使能; 所有PWM引脚翻转频率为150kHz; 所有I/O引脚悬空;(2) IDLE模式: Flash掉电; XCLKOUT关闭; eCAN-A、SCI-A、SPI-A、I2C等外设时钟使能; (3) STANDBY模式: Flash掉电; 所有外设时钟关闭; (4) HALT模式: Flash掉电; 所有外设时钟关闭; 禁止输入时钟输入。

e 如果一个石英晶振或者陶瓷谐振器被用作时钟源,HALT模式将关闭内部振荡器。

#### 6.2 频率/周期

表 6-2 频率/周期

|                           |                     | 衣 0-2                                                                                                                                                                             |      |     |     |  |

|---------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|--|

|                           |                     | 测试条件                                                                                                                                                                              | 极限   | 值   |     |  |

| 特性                        | 符号                  | 除另有规定,-55℃≤TA≤125℃,<br>V <sub>DDA2</sub> ,V <sub>DDAIO</sub> ,V <sub>DDIO</sub> ,<br>V <sub>DD3VFL</sub> =3.3V<br>V <sub>DD1A18</sub> ,V <sub>DD2A18</sub> ,V <sub>DD</sub> =1.8V | 最小   | 最大  | 单位  |  |

|                           |                     | 时钟                                                                                                                                                                                |      |     |     |  |

| 片载振荡器时钟                   | t                   | 时钟周期                                                                                                                                                                              | 28.6 | 50  | ns  |  |

| 万 郑 派 初 稻 印 TT            | $t_{C(OSC)}$        | 时钟频率                                                                                                                                                                              | 20   | 35  | MHz |  |

|                           |                     | 时钟周期                                                                                                                                                                              | 20   | 250 | ns  |  |

| 输入时钟XCLKIN                | tc(CI)              | 时钟频率                                                                                                                                                                              | 4    | 50  | MHz |  |

| 相人们,扩展CLKIIV              |                     | 时钟周期 <sup>a</sup>                                                                                                                                                                 | 6.67 | 20  | ns  |  |

|                           |                     | 时钟频率 <sup>a</sup>                                                                                                                                                                 | 50   | 150 | MHz |  |

| 系统时钟SYSCLKOUT             | t <sub>C(SCO)</sub> | 时钟周期                                                                                                                                                                              | 6.67 | 500 | ns  |  |

| 次が同り I B I B C L K O O I  | C(SCO)              | 时钟频率                                                                                                                                                                              | 2    | 150 | MHz |  |

|                           | _                   | 时钟周期                                                                                                                                                                              | 20   | 250 | ns  |  |

| 输出时钟XCLKOUT               | t <sub>C(XCO)</sub> | 时钟频率                                                                                                                                                                              | 4    | 50  | MHz |  |

| AHI LII I I ACLKOOT       | C(XCO)              | 时钟周期 <sup>a</sup>                                                                                                                                                                 | 6.67 | 20  | ns  |  |

|                           |                     | 时钟频率 <sup>a</sup>                                                                                                                                                                 | 50   | 150 | MHz |  |

| 高速外设时钟HSPCLK              | tagras              | 时钟周期                                                                                                                                                                              | 6.67 |     | ns  |  |

| 同处/ 及时 // HSI CLK         | t <sub>C(HCO)</sub> | 时钟频率                                                                                                                                                                              | _    | 150 | MHz |  |

| 低速外设时钟LSPCLK <sup>b</sup> | tag as              | 时钟周期                                                                                                                                                                              | 13.3 |     | ns  |  |

| 队还介区的 ササヒSPCLK            | $t_{C(LCO)}$        | 时钟频率                                                                                                                                                                              | _    | 75  | MHz |  |

<sup>&</sup>lt;sup>a</sup>仅包含数字IO端口,但不适用于GPIO32(SDAA)GPIO33(SCLA)配置为I2C模式。

$<sup>^{\</sup>mathrm{b}}$ A4分组样品大小(接收数)指器件引线数,至少3只器件,仅在初始鉴定、设计或工艺更改时进行。

d<sub>IDD</sub>包含Flash的电流;I<sub>DDIO</sub>电流依赖于I/O引脚的负载;I<sub>DDAI8</sub>包含V<sub>DDIAI8</sub>,V<sub>DD2AI8</sub>两个引脚的电流;I<sub>DDA33</sub>包含V<sub>DDA2</sub>,V<sub>DDAIO</sub>两个引脚的电流。

| 模数转换模块ADC时钟     | +                      | 时钟周期 | 40 | _  | ns  |  |

|-----------------|------------------------|------|----|----|-----|--|

| (快致科// 快以ADC的 针 | <sup>L</sup> C(ADCCLK) | 时钟频率 |    | 25 | MHz |  |

|                 |                        |      |    |    |     |  |

注电压均以Vss为基准,Vss=0V。电流以流入器件引出端为正。

## 6.3 输入输出时钟特性

表 6-3 输入输出时钟特性

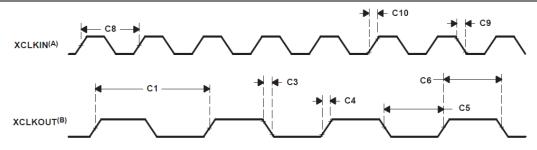

| 特性     符号     係另有规定,-55°C≤Ta≤125°C,VDDAIO,VDDIO,VDD3VFL=3.3V VDDIAI8,VDD=1.8V     最小 最大     单位       输入时钟频率     输入时钟频率     4     50     MHz       输入时钟频率 <sup>a</sup> 50     150     MHz       Limp模式SYSCLKOUT频率     f <sub>1</sub> /2启用时     1     5     MHz       XCLKIN时序-PLL启用     XCLKIN时钟周期     t <sub>C(CI)</sub> 见图6-1的C8     33.3     200     ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 特別       VDDA2, VDDAIO, VDDIO, VDD3VFL=3.3V VDD218, VDD=1.8V       最小 最大       基大                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| VDDIA18, VDD2A18, VDD=1.8V       输入时钟频率     输入时钟频率       输入时钟频率 <sup>a</sup> 4       Limp模式SYSCLKOUT频率     f1       /2启用时     1       XCLKIN时序-PLL启用                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 输入时钟频率       fx       外部振荡器/时钟源(XCLKIN)       4       50       MHz         输入时钟频率 <sup>a</sup> 50       150       MHz         Limp模式SYSCLKOUT频率       f1       /2启用时       1       5       MHz         XCLKIN时序—PLL启用                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 输入时针频率       fx       外部振荡器/时钟源(XCLKIN)       50       MHz         输入时钟频率 <sup>a</sup> 50       150       MHz         Limp模式SYSCLKOUT频率       f1       /2启用时       1       5       MHz         XCLKIN时序-PLL启用                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| f <sub>X</sub> 外部振荡器/时钟源(XCLKIN) 50 150 MHz Limp模式SYSCLKOUT频率 f <sub>1</sub> /2启用时 1 5 MHz XCLKIN时序—PLL启用                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Limp模式SYSCLKOUT频率 f <sub>1</sub> /2启用时 1 5 MHz XCLKIN时序—PLL启用                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| XCLKIN时序—PLL启用                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| XCI KIN时钟周期   tccn   见图6-1的C8   33.3   200   ne                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ACAMITES VI (PS) 70 (CI) /0 (DISTRICT DE SOL |

| XCLKIN下降沿时间t <sub>f(CI)</sub> 见图6-1的C9—6ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| XCLKIN上升沿时间t <sub>r(CI)</sub> 见图6-1的C10—6ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| XCLKIN低电平占空比 <sup>b</sup> t <sub>w(CIL)</sub> 45 55 %                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| XCLKIN高电平占空比 <sup>b</sup> t <sub>w(CIH)</sub> 45 55 %                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| XCLKIN时序-PLL禁用                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| XCLKIN时钟周期         t <sub>C(CI)</sub> 见图4-1的C8         20         250                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| XCLKIN下降沿时间 $t_{f(CI)}$ 见图6-1的C9 小于等于30MHz — 6 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

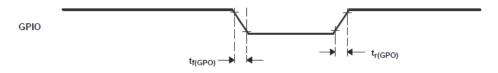

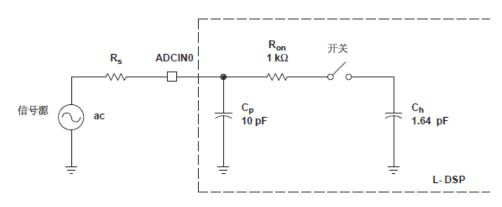

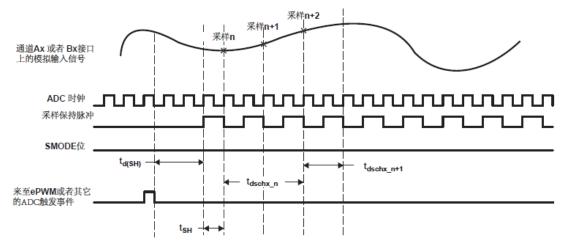

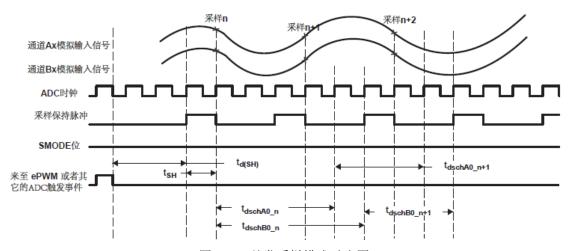

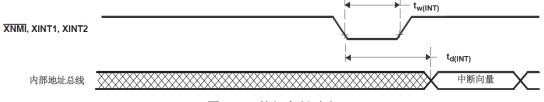

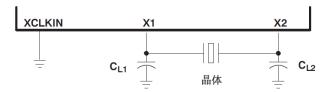

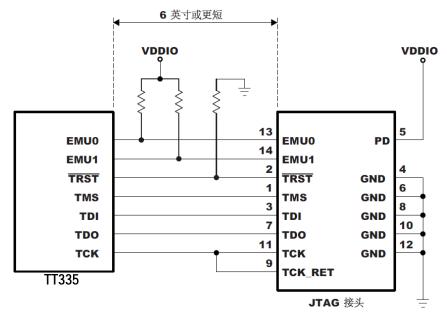

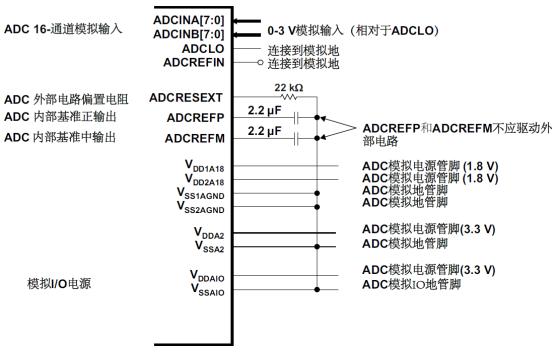

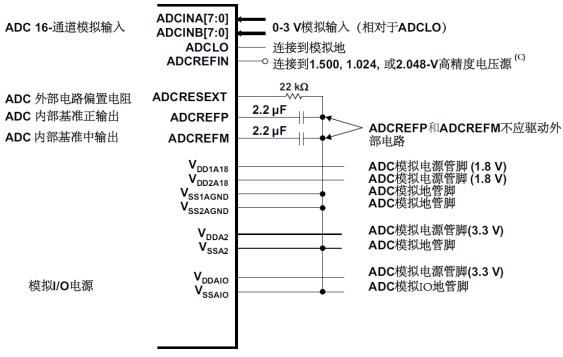

| XCLKIN上升沿时间t <sub>r(CI)</sub> 见图6-1的C10小于等于30MHz—6ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |